# VHDL Quick Start

Peter J. Ashenden The University of Adelaide

> Abridged by Roozbeh Jafari rjafari@cs.ucla.edu

## Modeling Digital Systems

- VHDL is for writing models of a system

- Reasons for modeling

- requirements specification

- documentation

- testing using simulation

- formal verification

- synthesis

- Goal

- most reliable design process, with minimum cost and time

- avoid design errors!

© 1998, Peter J. Ashenden

VHDL Quick Start

Modeling Interfaces

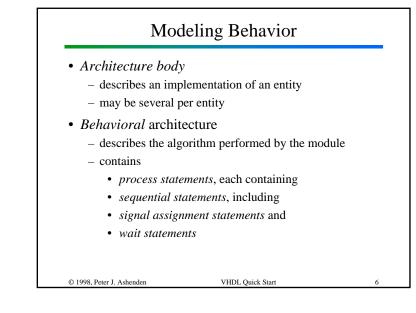

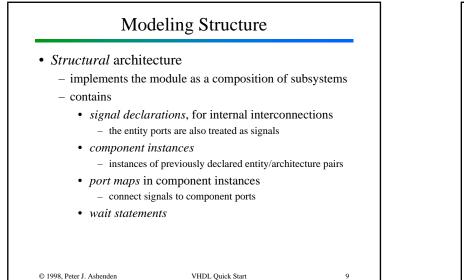

### **Basic VHDL Concepts**

VHDL Quick Start

- Interfaces

- Behavior

- Structure

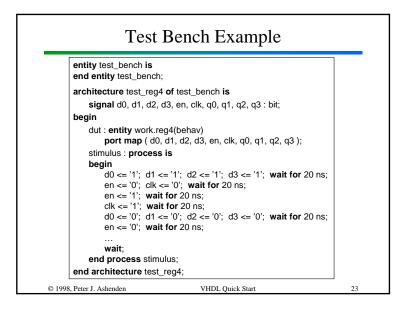

- Test Benches

- Analysis, elaboration, simulation

- Synthesis

© 1998, Peter J. Ashenden

• Entity declaration - describes the input/output *ports* of a module entity name port names port mode (direction) entity reg4 is port (d0, d1, d2, d3, en, clk : in bit; q0, q1, q2, q3 : **out** bit ); ----- punctuation end entity reg4; reserved words port type © 1998, Peter J. Ashenden VHDL Quick Start

|                       | navior Example                              |

|-----------------------|---------------------------------------------|

| architecture behav of | f reg4 <b>is</b>                            |

| begin                 | - 5                                         |

| storage : process     | is                                          |

| variable stored       | d_d0, stored_d1, stored_d2, stored_d3 : bit |

| begin                 |                                             |

| if en = '1' and       | clk = '1' then                              |

| stored_d0             | := d0;                                      |

| stored_d1             | := d1;                                      |

| stored_d2             | ,                                           |

| stored_d3             | := d3;                                      |

| end if;               |                                             |

| q0 <= stored_c        |                                             |

| q1 <= stored_c        |                                             |

| q2 <= stored_c        |                                             |

| q3 <= stored_c        |                                             |

| ,                     | , d2, d3, en, clk;                          |

| end process stora     |                                             |

| end architecture beha | av;                                         |

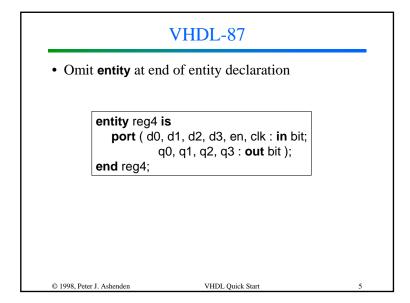

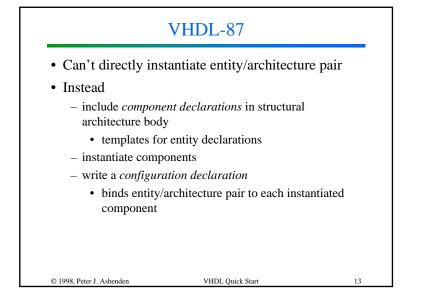

## VHDL-87

- Omit architecture at end of architecture body

- Omit is in process statement header

|                           | architecture behav of reg4 is<br>begin<br>storage : process<br><br>begin<br><br>end process storage;<br>end behav; |   |

|---------------------------|--------------------------------------------------------------------------------------------------------------------|---|

| © 1998, Peter J. Ashenden | VHDL Quick Start                                                                                                   | 8 |

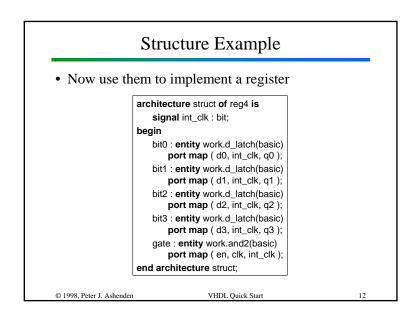

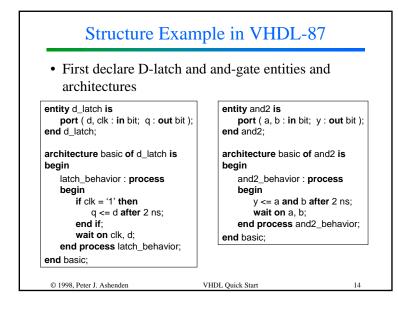

| Structur                                                                                                                                                                | e Example                                                                                                                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| • First declare D-latch an architectures                                                                                                                                | nd and-gate entities and                                                                                                                  |

| entity d_latch is<br>port ( d, clk : in bit; q : out bit );<br>end entity d_latch;                                                                                      | entity and2 is<br>port ( a, b : in bit; y : out bit );<br>end entity and2;                                                                |

| architecture basic of d_latch is begin                                                                                                                                  | architecture basic of and2 is begin                                                                                                       |

| latch_behavior : process is<br>begin<br>if clk = '1' then<br>q <= d after 2 ns;<br>end if;<br>wait on clk, d;<br>end process latch_behavior;<br>end architecture basic; | and2_behavior : process is<br>begin<br>y <= a and b after 2 ns;<br>wait on a, b;<br>end process and2_behavior;<br>end architecture basic; |

| © 1998, Peter J. Ashenden                                                                                                                                               | VHDL Quick Start 11                                                                                                                       |

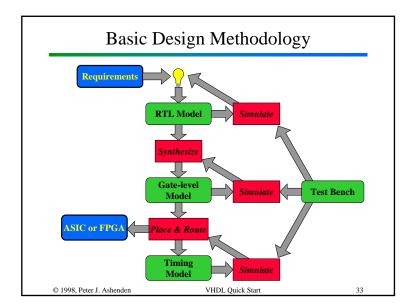

#### Synthesis

- Translates register-transfer-level (RTL) design into gate-level netlist

- Restrictions on coding style for RTL model

- Tool dependent – Altera, Xilinx

© 1998, Peter J. Ashenden

VHDL Quick Start

32